Курсовая работа: Устройство разделения цифрового потока данных

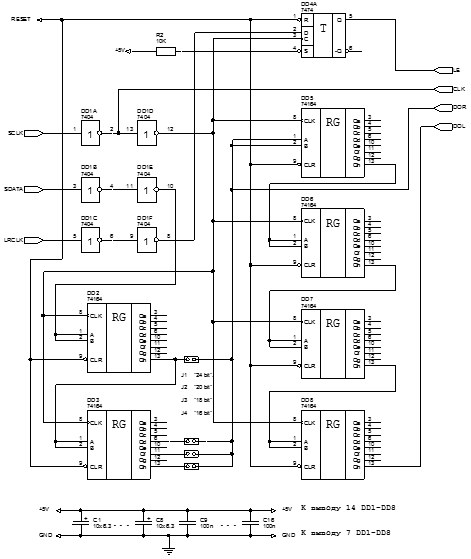

Входы и выходы на схеме обозначены так, как они обычно обозначаются у готовых микросхем цифровых фильтров.

Для обеспечения устойчивости данных во время загрузки, сигнал CLK для микросхем ЦАП инвертирован относительно сигнала SCLK, по которому происходит загрузка данных в регистры и сдвиг. Это позволяет загрузить данные в микросхемы ЦАП в тот момент, когда на выходах регистров получены устойчивые состояния данных. Для того чтобы при этом не возникало смещения между сигналом LE и DOR/DOL, сигнал LRCLK тактируется сигналом SCLK. Для этого используется D-триггер 74HC74, функциональным аналогом которого является микросхема К155ТМ2. Также в связи с подачей на микросхемы ЦАП инвертированного сигнала SCLK возникает необходимость обеспечить дополнительное смещение всей последовательности входных данных еще на один клок.

Рис. 10. – схема электрическая принципиальная устройства разделения данных для подключения микросхемы ЦАП AD1851

На входе установлены буферы на микросхеме 74HC04, время распространения сигнала для которой составляет 8nS, что является достаточно малой величиной и не отражается на быстродействии устройства в целом.

Конденсаторы C1-C16 устанавливаются непосредственно возле выводов питания микросхем. C1-C8 – конденсаторы с твердым электролитом SANYOOs-ConSA 10mx 6.3V, С9-С16 – керамические конденсаторы для поверхностного монтажа типоразмера 1206, емкостью 100n и группой ТКЕ X7R. Такой выбор обусловливает максимальную эффективность подавления помех по питанию при сохранении относительно невысокой стоимости устройства.

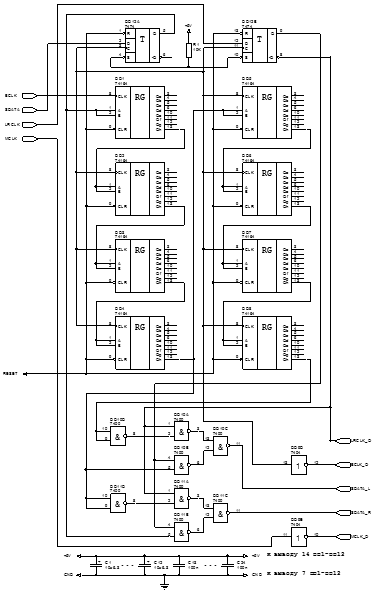

2.2.2 Схема устройства разделения потока данных для монофонического подключения микросхемы ЦАП AD1852 (AD1853)

Рис. 11. – схема электрическая принципиальная устройства разделения данных для монофонического подключения микросхемы ЦАП AD1852 (AD1853)

Входы и выходы на схеме обозначены подобно обозначениям на схеме из документации на AD1852.

Для обеспечения устойчивости данных во время загрузки, сигнал BCLK_O для микросхем ЦАП инвертирован относительно сигнала BCLK, по которому происходит загрузка данных в регистры и сдвиг. Это позволяет загрузить данные в микросхемы ЦАП в тот момент, когда на выходах регистров получены устойчивые состояния данных. Для того чтобы при этом не возникало смещения между сигналом LRCLK и SDATA_L/SDATA_R, сигнал LRCLK тактируется сигналом BCLK. Мультиплексоры на микросхемах DD10, DD11 управляются уже тактированным сигналом LRCLK. Для этого используется D-триггер 74HC74, функциональным аналогом которого является микросхема К155ТМ2. Поскольку AD1852(AD1853) также использует сигнал MCLK (128Fs/256Fs/384Fs), который связан с сигналом BCLK, сигнал MCLK_O также инвертирован. Также в связи с подачей на микросхемы ЦАП инвертированного сигнала SCLK возникает необходимость обеспечить дополнительное смещение всей последовательности входных данных еще на один клок, что выполняется D-триггером DD12A.

При необходимости на входе устанавливаются буферные элементы.

Конденсаторы C1-C24 устанавливаются непосредственно возле выводов питания микросхем. C1-C12 – конденсаторы с твердым электролитом SANYOOs-ConSA 10mx 6.3V, С13-С24 – керамические конденсаторы для поверхностного монтажа типоразмера 1206, емкостью 100n и группой ТКЕ X7R. Такой выбор обусловливает максимальную эффективность подавления помех по питанию при сохранении относительно невысокой стоимости устройства.

2.2.3 Общие замечания к схемам

Вход схем RESET подключается к генератору сброса системы. Активным уровнем сброса является уровень логического "0". Данный узел может быть выполнен, к примеру, на микросхеме ADM707.

Несмотря на то, что микросхемы ЦАП часто имеют питание цифровой части 5 V, имеет смысл выделить для них отдельный источник питания, а не использовать один источник для схемы разделения цифрового потока и ЦАП одновременно. Это позволит уменьшить уровень помех, проникающих из цифровой части микросхемы ЦАП в аналоговую часть устройства и улучшит звучание системы.

Часть 3. Временные диаграммы

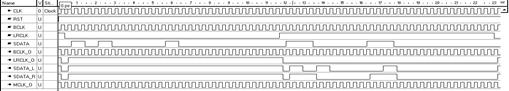

3.1 Временная диаграмма работы устройства разделения данных для микросхемы ЦАП AD1851

Рис. 12. - Временная диаграмма работы устройства разделения данных для микросхемы ЦАП AD1851

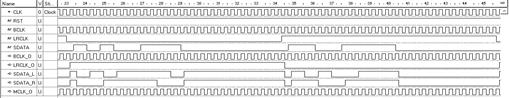

3.2 Временная диаграмма работы устройства разделения данных для микросхемы ЦАП AD1852

Рис. 13. - Временная диаграмма работы устройства разделения данных для микросхемы ЦАП AD1852

Часть 4. Реализация схемы в проекте VHDL

Поскольку полученные схемы не всегда удобно размещать в конечном устройстве ввиду их громоздкости, имеет смысл создать проект на языке VHDL и составить код для программирования кристалла ПЛМ. Помимо значительного сокращения занимаемой на плате площади это позволит также поднять общее быстродействие модуля разделения потоков данных, снизить наводимые цифровые помехи, промоделировать устройство без пайки.

Коды на языке VHDL представлены ниже с краткими пояснениями, где это необходимо.

Для начала выберем необходимые компоненты и составим их модели:

--Components.vhd

--16-bit Serial to Parallel Shift Register with asynchronous reset

library ieee ;

use ieee.std_logic_1164.all ;

entity SPREG16R is