Курсовая работа: Устройство разделения цифрового потока данных

В некоторых случаях необходимо принимать данные не в формате Right Justifited, а в формате I2S. Такая необходимость возникает при построении ЦАП не в виде отдельного модуля, а как части готового проигрывателя компакт-дисков или какого-либо другого цифрового аудио устройства. Помимо того данный формат передачи обязательно поддерживается цифровыми приемниками и интерфейсными микросхемами. Таким образом, один раз грамотно спроектированное решение для подключения непосредственно на шину I2S будет не только наиболее правильным, а и наиболее универсальным. Устройство на основе такого решения уже целесообразно выполнить в виде ПЛМ и в дальнейшем использовать как некий "черный ящик" выполняющий все необходимые процедуры.

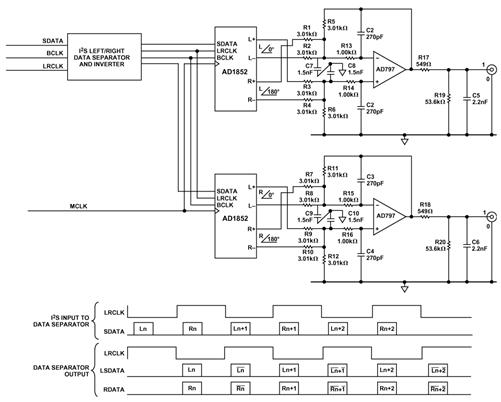

Рассмотрим формат передачи данных I2S:

Рис. 6. – формат передачи данных I2S

В этом формате данные левого и правого каналов передаются последовательно по одному проводнику SDATA, данные какого именно канала передаются в данный момент, определяет состояние сигнала LRCLK, тактовые импульсы передаются посредством сигнала SCLK. Первыми передаются данные левого канала (LRCLK=’0’), затем правого (LRCLK=’1’). Данные поступают в формате MSBFirst, и выровнены относительно перепада сигнала LRCLK по левому (переднему) фронту и задержаны на 1 тактовый импульс.

Легко заметить, что данный формат отличается от Right Justifited лишь выравниванием последовательности данных и инвертированным состоянием сигнала LRCLK. Таким образом, для преобразования формата I2S к формату Right Justifited достаточно задержать всю последовательность данных на (32-[разрядность ЦАП]-1) тактовых импульса и инвертировать сигнал, определяющий данные какого канала передаются в настоящий момент. Далее можно использовать уже имеющийся вариант со сдвиговым регистром.

С учетом того, что минимальная разрядность современных микросхем аудио ЦАП составляет 16 бит, использование 16 битного сдвигового регистра позволяет выбором перемычки осуществлять подключение ЦАП любой разрядности (от 16 до 24 бит) к 16 битному источнику данных без потери качества. Также возможно подключение источника сигнала большей разрядности к микросхеме ЦАП меньшей разрядности с потерей только младших бит данных, что в некоторых случаях также может оказаться удобным, поскольку дает совместимость с новыми форматами.

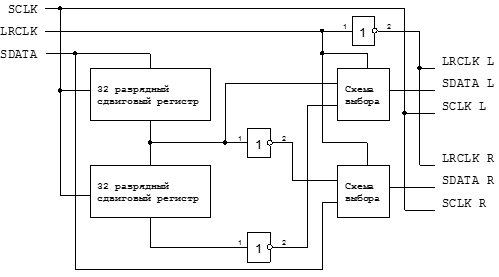

Структурная схема такого преобразователя форматов данных представлена на следующем рисунке:

Рис. 7. – универсальный сдвиговый регистр

1.2.2 Подключение микросхемы ЦАП AD1852 (AD1853)

Микросхема ЦАП AD1852 представляет собой стереофонический дельта-сигма ЦАП с встроенным цифровым фильтром и выходом по напряжению. AD1853 отличается от нее лишь токовым выходом. Данные микросхемы поддерживают все существующие на сегодняшний день наиболее популярные аудио форматы, включая 24bit 192kHz, что делает их очень удобным решением для построения универсального модуля ЦАП пригодного как для высококачественного прослушивания аудио компакт-дисков, так и для просмотра фильмов в формате DVD.

Микросхемы изначально имеют достаточно высокие качественные параметры и подключаются напрямую к шине I2S. Тем не менее, при желании получения максимального возможно качества, возможно дополнительное улучшение характеристик конечного устройства путем применения монофонического включения данных микросхем. При этом необходимо в каждую микросхему дважды загружать данные соответствующего ей канала, первый раз в исходном виде, второй раз в инвертированном. Так же, как и в случае с подключением AD1851, необходимо следить за одновременностью поступления данных обоих каналов.

Монофоническое подключение микросхемы AD1852 показано на следующем рисунке (взято из файла технической документации от AnalogDevices):

Рис. 8. – монофоническое подключение AD1852

Для осуществления необходимых манипуляций над данными составим устройство на основе регистра сдвига. Его общая структурная схема приведена на рис. 9. Как видно из временной диаграммы работы, максимальный интервал времени, на протяжении которого необходимо сохранять данные, составляет 1 фрейм, или 1 период сигнала LRCLK, или 64 периода сигнала SCLK. При этом инвертированные данные сдвинуты на 32 периода сигнала SCLK относительно данных исходных. Данные разделяются следующим образом:

· Данные снимаются одновременно с несколькими временными задержками, нужная порция данных выбирается схемой выборки

Рис. 9. – структурная схема устройства разделения данных

· В тот момент времени, когда на входной шине передаются данные правого канала, на выходе первого 32 разрядного сдвигового регистра будут находиться данные левого канала

· Во время передачи на входной шине данных левого канала на выходе первого сдвигового регистра будут данные правого канала предыдущего отсчета, а на выходе второго регистра еще только данные левого канала предыдущего отсчета

· Какие именно данные подавать на выходные шины, определяет схема выборки (также по 1й на каждый канал)

· Управление инверторами и схемами выборки осуществляется от сигнала LRCLK

· Сам сигнал LRCLK на выходные шины поступает в инвертированном виде

Часть 2. Схемная реализация

2.1 Определение требований к применяемым цифровым микросхемам

Поскольку обработка данных происходит лишь выбором необходимой последовательности и не предполагает непосредственного изменения битов информации в каждой посылке, данное устройство не вносит искажений в выходной сигнал блока ЦАП прямым образом. Тем не менее, следует учитывать, что музыкальный сигнал определяется не только содержанием пакетов данных, а и временем их прихода. Таким образом, необходимо учитывать частотные свойства применяемых микросхем. Необходимое минимальное быстродействие регистров составляет 64Fs, а лучше иметь запас в 3-4 раза. Для сигналов при просмотре фильмов в формате DVDFs составляет 192 KHz. Следовательно, регистры должны работать с частотами не менее 13 MHz. С учетом желательности запаса по быстродействию, следует выбирать микросхемы, способные работать на частотах 40 MHz и выше.

Важно помнить, что данные на шине SDATA являются правильными во время нарастающего фронта импульса SCLK. Следовательно, загрузку в регистр необходимо также производить по нарастающему фронту.

Также при проектировании необходимо учитывать, что устройство должно быть легко повторяемым, т.е. желательно отказаться от применения дефицитных компонентов. В данном случае, проблема затрагивает только выбор сдвиговых регистров. Поскольку наиболее легкодоступными являются регистры длиной 8 бит, именно их имеет смысл использовать при построении устройства.

Еще одним фактором, влияющим на выбор микросхем, является то, что практически все современные микросхемы ЦАП и цифровых приемников имеют входные и выходные цепи с КМОП уровнями.

С учетом всего, выше сказанного, останавливаемся на сдвиговом регистре 74HC164. Он представляет собой 8-битный сдвиговый регистр с параллельным выходом, выполненный по КМОП технологии и способный работать на частотах до 50 MHz. Функциональным аналогом данного регистра является микросхема К155ИР8.